超越摩爾定律的先進封裝

因應人工智能、高速通訊技術(5G、Wifi6)、高效資料中心、汽車電子…等新興科技產品需求,能夠達到高傳輸速度、高訊號品質,且低延遲的封裝技術將是非常重要的課題,這必須仰賴先進材料及不斷地精進製程設備的能力,方能突破至更微細的整體生產工藝。同時,新世代的製程設備除了製造出符合性能要求之外,進一步還須兼顧環保議題,為企業的永續盡一份力。

凌嘉科技的薄膜濺鍍及電漿蝕刻平台以乾式環保製程為技術核心,除了設備能力能夠滿足客戶的要求,亦能提供客製化的自動化平台,達到高良率、高產能的最低生產成本(COO)之優勢。在半導體先進封裝領域中,我們至少擁有下述的設備應用知識與能力,並具有厚實的專業能力而能藉由相似的製程模式衍伸至其他的製程應用。

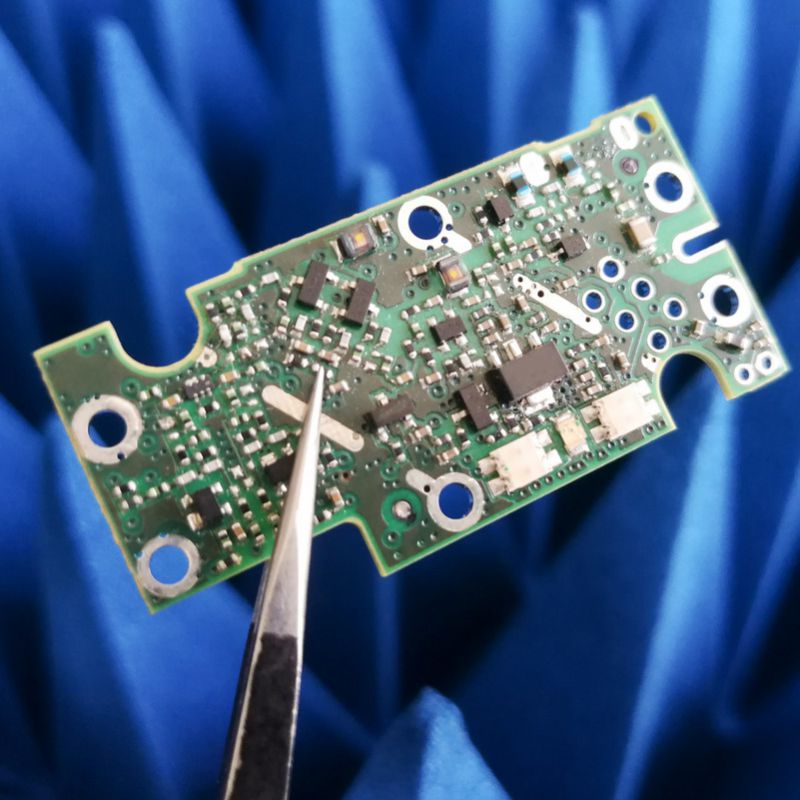

每個電子元件或其系統在運作時都會產生一定程度的電磁干擾 (EMI),這會對周邊電器的性能產生不利影響。因此,電子元件或其系統的電磁干擾必須受到限制,同時,對環境中的干擾也必須具有足夠的免疫力。

「抗電磁干擾屏蔽濺鍍」即是以乾式製程於電子元件的外表面以物理的方式附著上足夠厚度的屏蔽層,藉此達到電磁屏蔽的目的。

後摩爾定律(Moore‘s Law)時代,前段製程的研發及設備成本大幅提升,採用先進封裝以進一步提高晶片整合度並降低製造成本,已是半導體展業變革趨勢。

扇出型封裝技術包括FOWLP與FOPLP,共同點是能以扇出的形式形成較多的I/O引腳,藉此使單一晶片能整合更多功能,並達到薄型化及降低成本等優點。兩者主要差異在於生產時的載體不同,進而能依晶片用途而選擇於細線路尺寸及封裝成本之間的平衡。

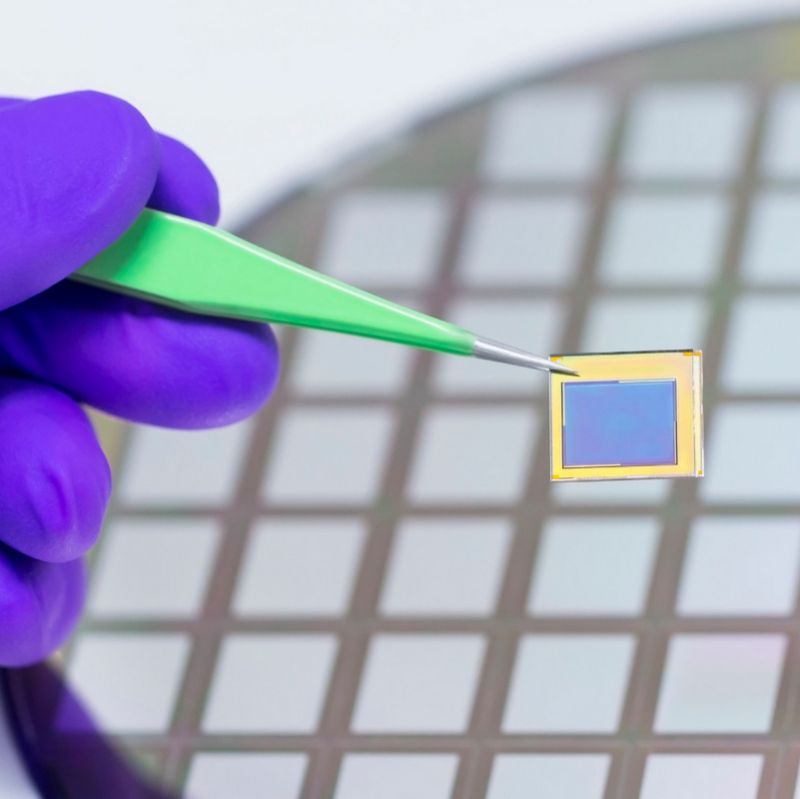

以先進半導體製程技術製造出的「已知良好裸晶(Know Good Die;KGD)」,通常擁有較高的線路密度,而必須藉由扇出(Fan out)的方式將線路接點(I/O Pad)自裸晶表面的狹小區域向外重新佈置,以利後續的晶片裝配。

重分佈線層(Redistribution Layer;RDL)即是利用晶圓等級的金屬佈線技術將線路接點外引至晶片外,同時達到更薄的封裝厚度及更優異的電性表現。

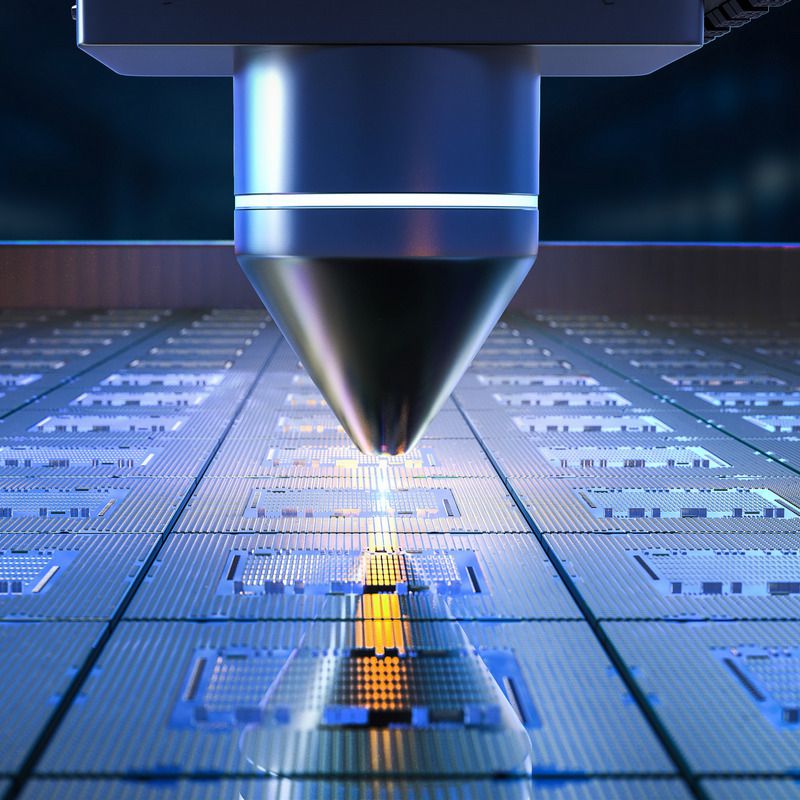

隨著智慧型手機、平板電腦和其他可攜式裝置的普及,對於輕薄且高效能的電子產品需求也越來越高,於縮小線寬線距的同時,線路的尺寸和形狀有越來越高的限制,這促使前瞻技術開發人員不斷探索更精密、更高效、更經濟的製程技術。

導入凌嘉科技高選擇比、高均勻性的蝕刻技術,能夠準確地去除多餘的金屬材料而不損害其他部分,進而製作出精確的電路圖形,進一步還能整合性能優異的薄膜濺鍍設備,解決金屬附著力、鍍膜均勻性等問題,提高產品良率及競爭力。

無導線電鍍金技術(Non Plating Line;NPL)提供了一種不需要在載板的表面佈設電鍍用導線,即可以對載板邊緣的接觸墊(Pad)進行電鍍鎳金的設計。其主要以導電膜作為電流傳導路徑以導通載板上的各接觸墊,進而對其進行電鍍鎳金的工藝與結構,可大幅度減少因電鍍導線的佈設而造成的影響。

晶背金屬化是在電子設備製造過程中,在半導體基板(如矽晶片)或IC的背面以真空濺鍍的方式沉積一層或多層金屬層的工藝。該金屬層可做為接合/導熱用的金屬層,也可再接合基材,用於改善散熱、提供電屏蔽並降低電阻。

晶背金屬化的濺鍍製程的優劣對於產品良率及半導體元件的可靠性影響很大,如果金屬層與產品接合度不佳會造成金屬層剝離與阻抗上升等問題。低歐姆接觸電阻和出色的薄膜附著力是背面金屬化工藝最關鍵的要求。

相較於有芯載板(Cored Substrate),無芯載板(Coreless Substrate)技術取消了作為核心層的玻纖布,而改以直接使用增層絕緣材料進行佈線封裝。

無芯載板技術藉由取消核心層而降低成本,此外因佈線能力的提高,使得錫球凸塊的佈局限制極小,並能達到良好的高速傳輸特性,於交流和直流功率特性均能得到改善。