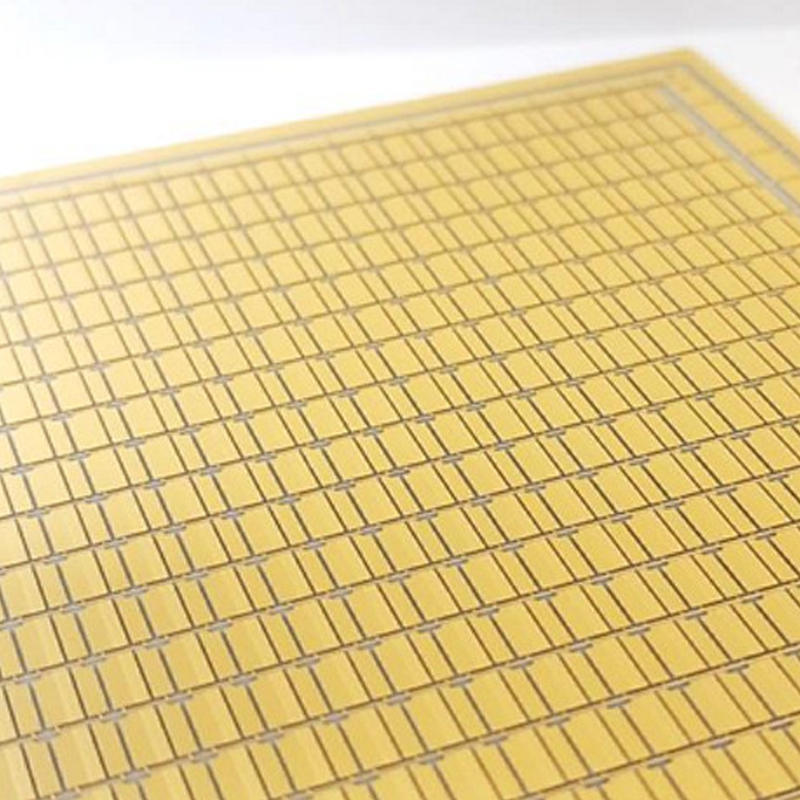

以先進半導體製程技術製造出的「已知良好裸晶(Know Good Die;KGD)」,通常擁有較高的線路密度,而必須藉由扇出(Fan out)的方式將線路接點(I/O Pad)自裸晶表面的狹小區域向外重新佈置,以利後續的晶片裝配。

重分佈線層(Redistribution Layer;RDL)即是利用晶圓等級的金屬佈線技術將線路接點外引至晶片外,同時達到更薄的封裝厚度及更優異的電性表現。

應用說明

隨著微縮技術的進步及晶片功能的複雜化,以先進半導體製程技術製造出的「已知良好裸晶(Know Good Die;KGD)」,因具有極高的電晶體密度及線路密度,而無法在裸晶的面積之內容納所有的接腳,必須藉由扇出(Fan out)的方式將線路接點(I/O Pad)自裸晶表面向外重新佈置,藉此符合封裝和其他電路的要求。

而將金屬線路接點外引的技術,即泛稱為重佈線層(Redistribution Layer;RDL)技術。於應用上又可依線寬間距(Line/Space;L/S)進一步分為:(1)晶圓廠的超細線路應用;(2)先進封裝廠的細線路應用;及(3)先進載板廠的細線路應用。

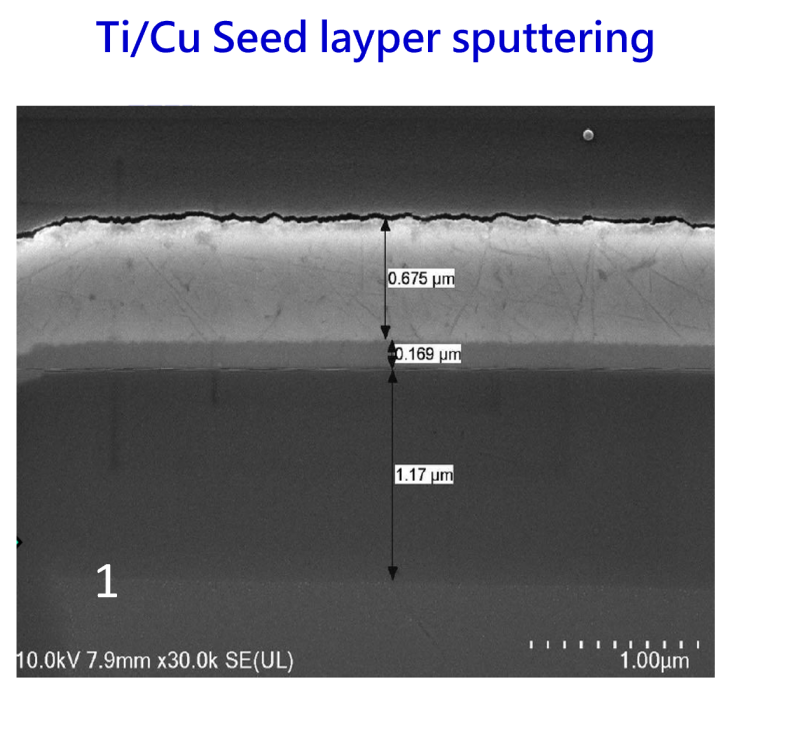

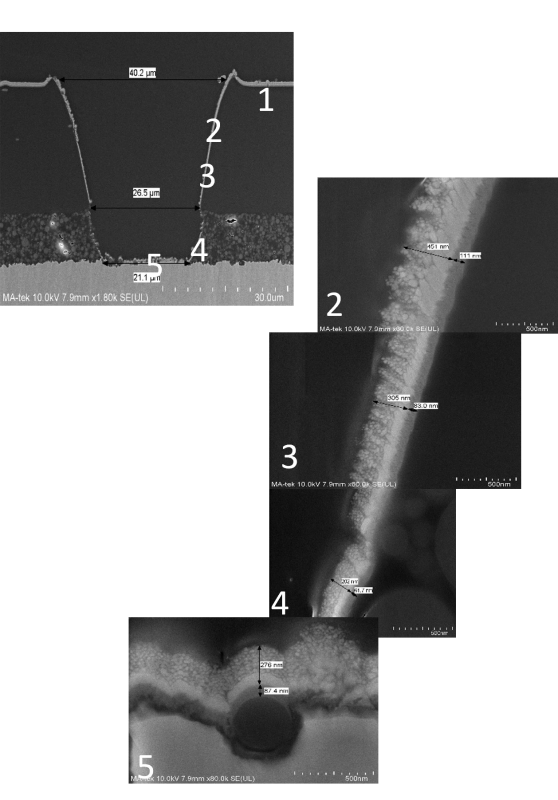

於不同的應用中,會採用不同製程解決方案來完成金屬導線的製作,例如利用光罩以曝光、顯影、蝕刻的方式製造出超細線路,或者是使用雷射光刻配合清潔、濺鍍金屬種子層、電鍍增厚金屬層、蝕刻去除金屬種子層的方式於基材上製造出金屬細線路。前者可達成超細線路的應用但設備成本較高而多見於晶圓廠,後者則通常用於封裝廠或載板廠。

進一步在ESG的政策響應下,後者也逐步從濕式製程轉換至乾式製程,例如基材的清潔方式改以乾式的電漿蝕刻清潔;而蝕刻去除種子層的方式,也從利用藥水的濕式製程逐步朝向以乾式電漿蝕刻的方式將其去除,藉此達到低材料消耗、低環境污染和簡單的後處理工序目的。

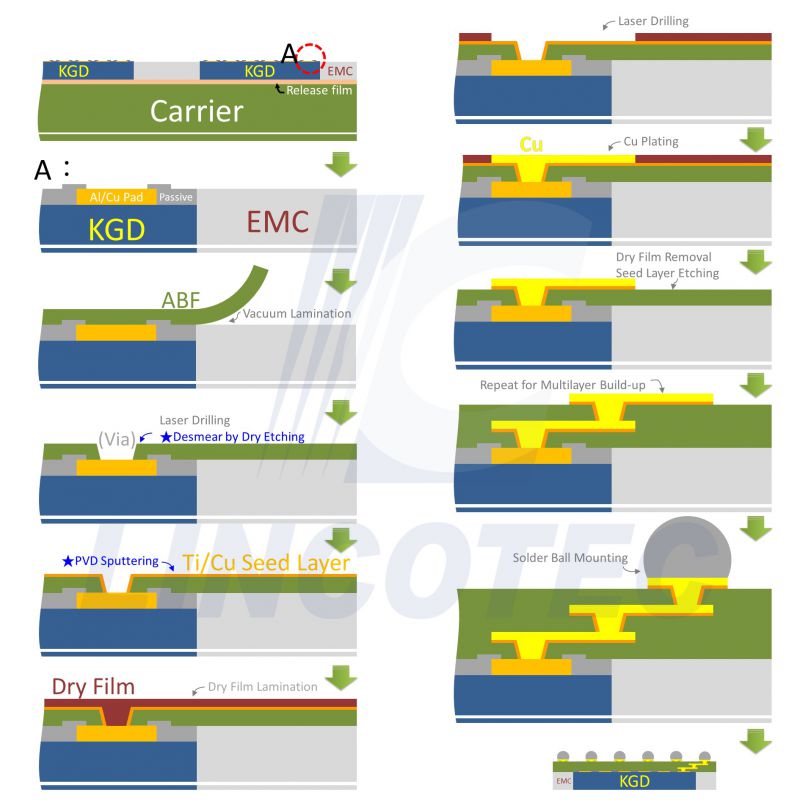

以下圖示說明先進封裝廠以ABF(Ajinomoto Build-up Film)作為基材時的Die-First/Face-up重佈線層製程:

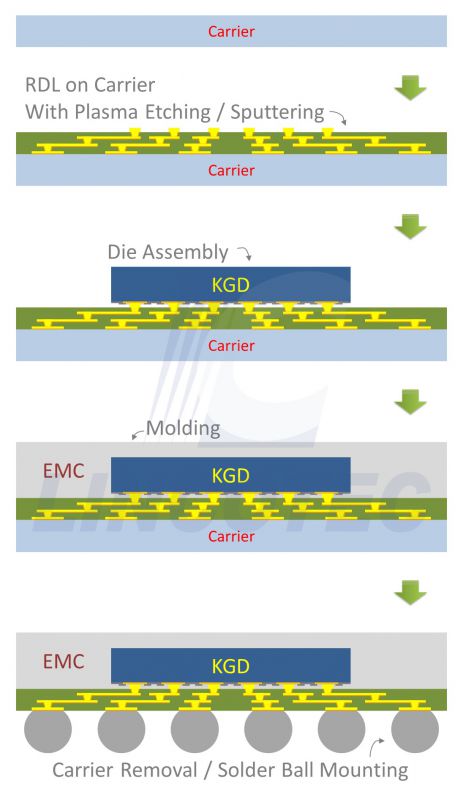

前述的Die Fisrt製程由於是直接先放置KGD之後,再對其進行重佈線。但這樣的製程可能因製程良率的風險而導致KGD的損壞,因此尚有另一種先完成RDL之後,再將KGD附著上去的Die-last製程,如下圖所示。雖然相較於Die-first製程,此方式需先以Carrier當作臨時的載體,再至將其移除後於同側附著錫球,製程步驟略為複雜,但能有效避免KGD的損失。

對此,凌嘉科技有自主的智慧財產權,能協同客戶進行製程開發及實驗驗證,尤其於重佈線層製程應用中,對於Desmear、Descum、Ti etching、Seel layer濺鍍…等技術有豐富的製程開發經驗,除了可以提供研發階段於不同製程配方下的打樣服務之外,亦擁有合格且高精密度的實驗室能進行樣品的測試。

凌嘉特色

專注於Sputter及Etching技術,掌握RDL的關鍵能力

實績