後摩爾定律(Moore‘s Law)時代,前段製程的研發及設備成本大幅提升,採用先進封裝以進一步提高晶片整合度並降低製造成本,已是半導體展業變革趨勢。

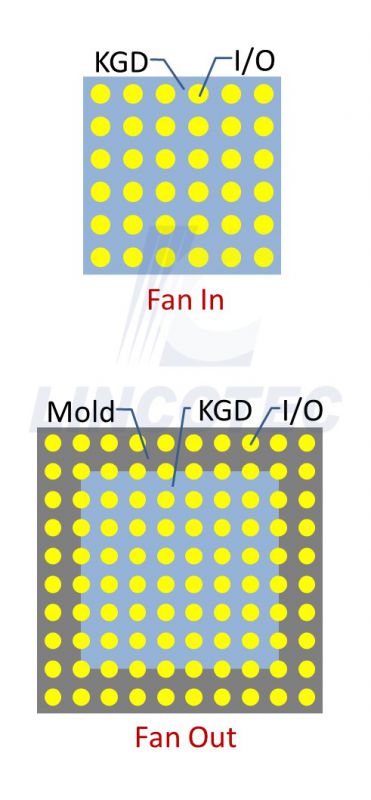

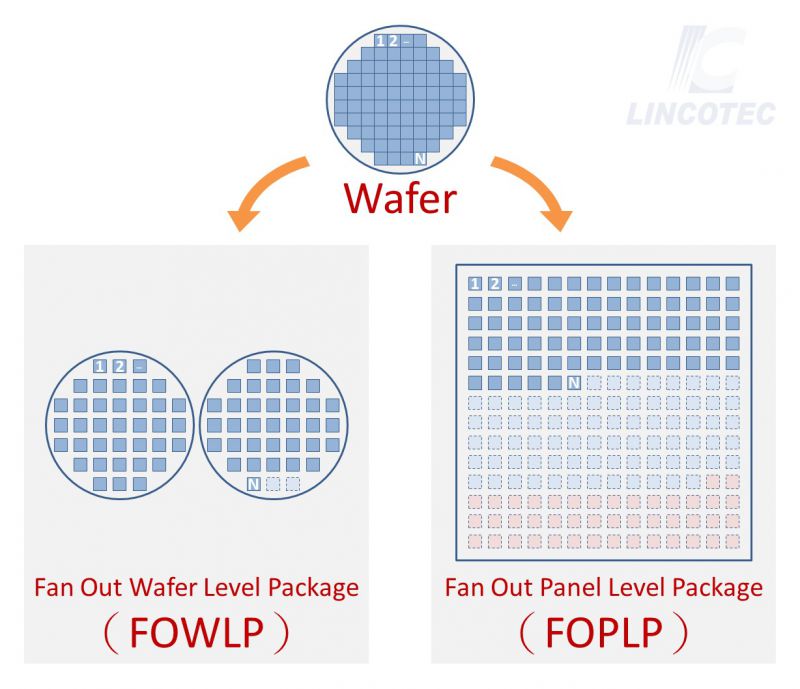

扇出型封裝技術包括FOWLP與FOPLP,共同點是能以扇出的形式形成較多的I/O引腳,藉此使單一晶片能整合更多功能,並達到薄型化及降低成本等優點。兩者主要差異在於生產時的載體不同,進而能依晶片用途而選擇於細線路尺寸及封裝成本之間的平衡。

應用說明

傳統的摩爾定律(Moore's law)通常被解讀為:單位面積的積體電路上可容納的電晶體數目約每隔2年會增加1倍;同樣運算速度的晶片價格則每2年會變成2分之1。但隨著晶圓製造廠(Foundry)的前段先進製程技術逐漸進入物理極限,且為超高資本投資,窮盡資源追求前段製程的微縮已非半導體產業的唯一手段。

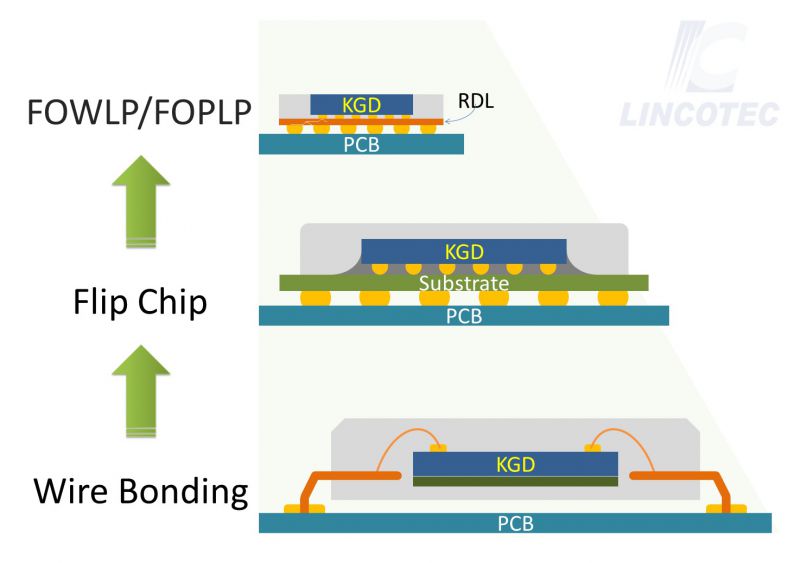

先進封裝製程的發展,自早期的打線接合技術(Wire Bonding) 、覆晶技術(Flip Chip) ,再到目前的扇形封裝技術(Fan Out),自是不斷嘗試使晶片能夠堆疊或縮小相鄰晶片的間距,而使晶片之間的金屬連線(Interconnect)距離變短,藉此縮小尺寸與縮短訊號傳輸距離而取得較佳的電性表現。

為達以上目的,還需藉由良好的製程流程規劃及設備參數以降低其線路阻抗(RC, Contact resistance)而進一步提高其性能及可靠度。如此方能滿足後摩爾時代於消費性電子產品不斷增長的需求,及提供定價時的有利PPAC指標:「高功率(Power)、高性能(Performance)、低晶片面積(Area)、低成本(Cost)」。

早期的打線接合技術是將IC晶片固定於導線架(Lead Frame)上,再以例如金線等焊線連接晶片與外引腳之間,其缺點除了必須「一根一根地」打線之外,由於導線架的金屬接腳只能製作在四周圍,所以當晶片的接腳需求提高時,將增加封裝體積且將提高焊線的材料成本,並不利用在日益要求重量、尺寸及多元功能的消費型電子產品上。

1960年代,美國IBM公司提出以覆晶形式的晶片接合方式,是先於矽晶片上以晶圓級構裝(Wafer Level Package;WLP)佈線,並採用Fan in設計形成位於晶片範圍內之金屬凸塊(Bump),及位於凸塊上的金屬焊材,此時。金屬焊材能加熱而形成球狀,進而當晶片與電路板連接時能依其物理性質而具自我校正位置的功效,藉此提高良率並用於細小節距(Fine Pitch)的產品上。由於覆晶技術具有高I/O密度、易於電磁遮蔽處理、低電感、封裝尺寸小等優點,已成為目前市占率最高之封裝技術。

進一步,德國英飛凌公司(Infineon Technologies)於2001年提出US6727576B2專利,為扇出型晶圓級封裝(Fan Out Wafer Level Package;FOWLP)技術之濫觴。節錄SEMI國際半導體產業協會於其官網之說明:「FOWLP技術是從半導體裸晶的端點上,向外拉出需要的電路至重分佈層(Redistribution Layer;RDL),進而形成封裝。其最大的特點在於:在尺寸相同的晶片下讓重分佈層範圍更廣,晶片腳數更多,單晶片可以整合更多功能,並達到無載板封裝、薄型化以及低成本等優點。若希望達到高密度量產的目標,重分佈層的技術應用將是關鍵。

扇出型晶圓級封裝的製程可分為以下兩種主流:

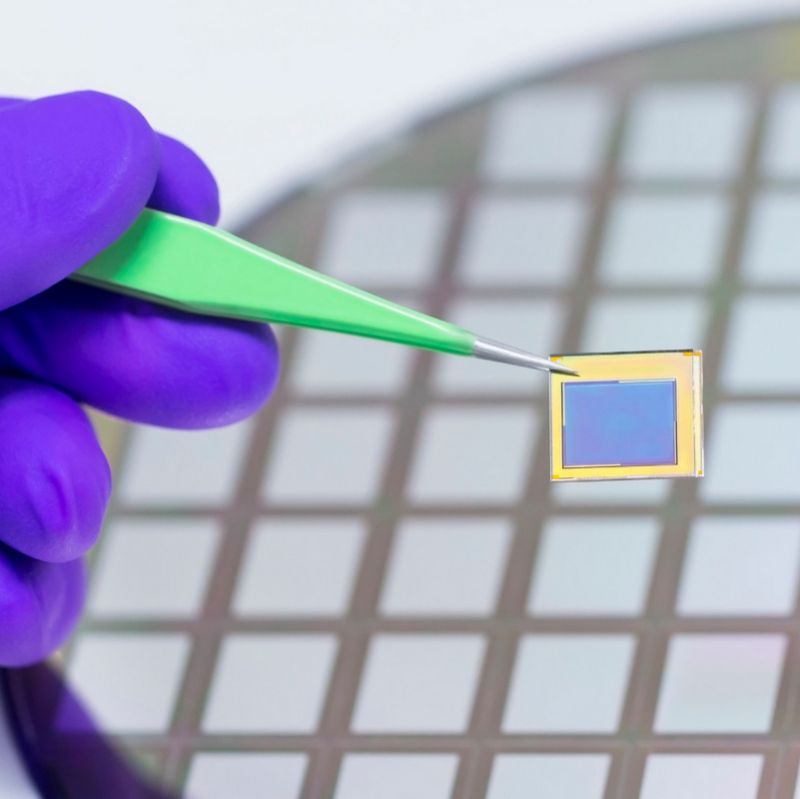

1.晶片優先Fan Out:於基板上放置,從原始裝置晶圓中挑揀出的合格晶元(Know Good Die;KGD),以模壓樹脂包覆成重構晶圓,再進一步處理成晶圓上的RDL。

2.RDL優先Fan Out:載具晶圓頂端建立RDL層並暫時接合,在頂端放置KGD然後研磨壓模與模具。

扇出型晶圓級封裝技術仍是基於前段半導體製程,惟因需提供向外扇出線路之空間,而必須將KGD重新取放(Pick and Place)至重構晶圓上,由於前後段製程能整合進行,相較於其他封裝技術,除了能降低製程生產與材料等成本之外,針對低線寬間距(Line Space;L/S),還能整合步進式曝光機(Stepper)或光罩對準曝光機(Mask Aligner)達到高精度要求。

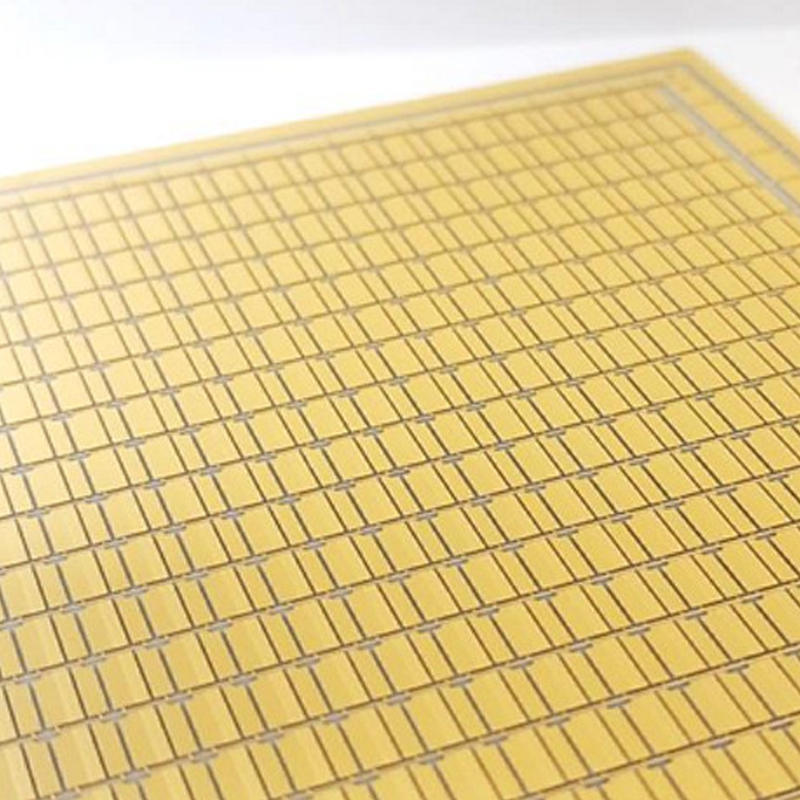

但並非所有的晶片於封裝時都會要求低線寬線距,此時考量選用更多元的封裝材料與成本更低的設備即為PPAC指標的關鍵。此外,每片重構晶圓能乘載的KGD數量有限,並不利於一次性的大量生產,因此衍生出了以面積更大的矩型載板,例如印刷電路板或是玻璃基板,作為載體進行扇出封裝製程的扇出型面板級封裝技術(Fan Out Panel Level Packaging;FOPLP)。

扇出型晶圓級封裝與扇出型面板級封裝同樣具備提升電氣性能與I/O密度、支援薄型化設計等優勢,並期望能藉由更大面積的生產進一步降低生產成本,從右圖可以明顯看出採用FOPLP時的產能優勢。

以下整理扇出型晶圓級封裝與扇出型面板級封裝的特點比較:

| 扇出型晶圓級封裝(FOWLP) | 扇出型面板級封裝(FOPLP) | |

|---|---|---|

| 每片產能 | 受限於重構晶圓的尺寸,產能較低。 | 產能較高,以12吋晶圓與700x700mm2的載具相比較, 載具單次的產量約為晶圓的7.8倍。 |

| 應用領域 | I/O高密度要求之晶片,例如:CPU、GPU、 AP、ASIC、FPGA、AiP等。 | I/O密度要求較低之晶片,例如:PMIC、APE、MEMS、Sensor等。 |

| 設備需求 | 多採用較精密的先進製程設備,成本較高。 | 對於製程設備的精度要求相對較低,成本較低。 |

| 線寬線距 | L/S<5/5 | L/S≥5/5 |

| RDL層數 | 可達5層以上 | 多用於4層以下 |

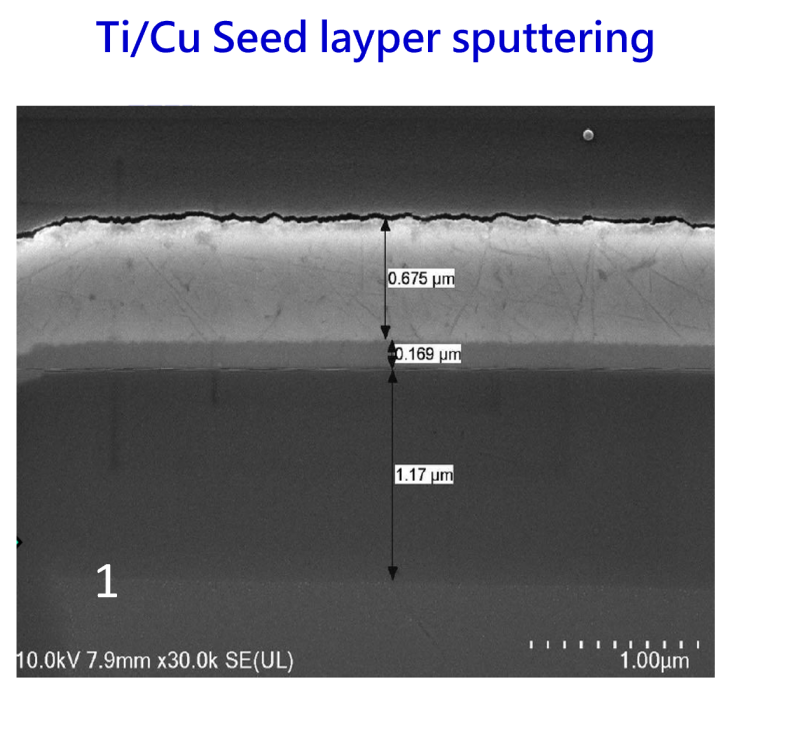

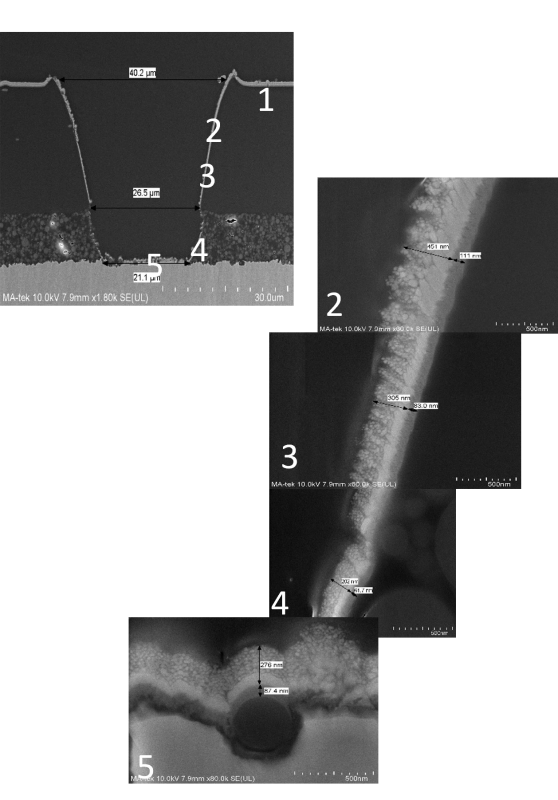

對此,凌嘉科技有自主的智慧財產權,能協同客戶進行製程開發及實驗驗證,尤其於FOPLP領域中,對於Desmear、Descum、Ti etching、Seel layer濺鍍…等技術有豐富的製程開發經驗,除了可以提供研發階段於不同製程配方下的打樣服務之外,亦擁有合格且高精密度的實驗室能進行樣品的測試。

凌嘉特色

專注於Sputter及Etching技術,掌握FOPLP的關鍵能力

實績