隨著智慧型手機、平板電腦和其他可攜式裝置的普及,對於輕薄且高效能的電子產品需求也越來越高,於縮小線寬線距的同時,線路的尺寸和形狀有越來越高的限制,這促使前瞻技術開發人員不斷探索更精密、更高效、更經濟的製程技術。

導入凌嘉科技高選擇比、高均勻性的蝕刻技術,能夠準確地去除多餘的金屬材料而不損害其他部分,進而製作出精確的電路圖形,進一步還能整合性能優異的薄膜濺鍍設備,解決金屬附著力、鍍膜均勻性等問題,提高產品良率及競爭力。

應用說明

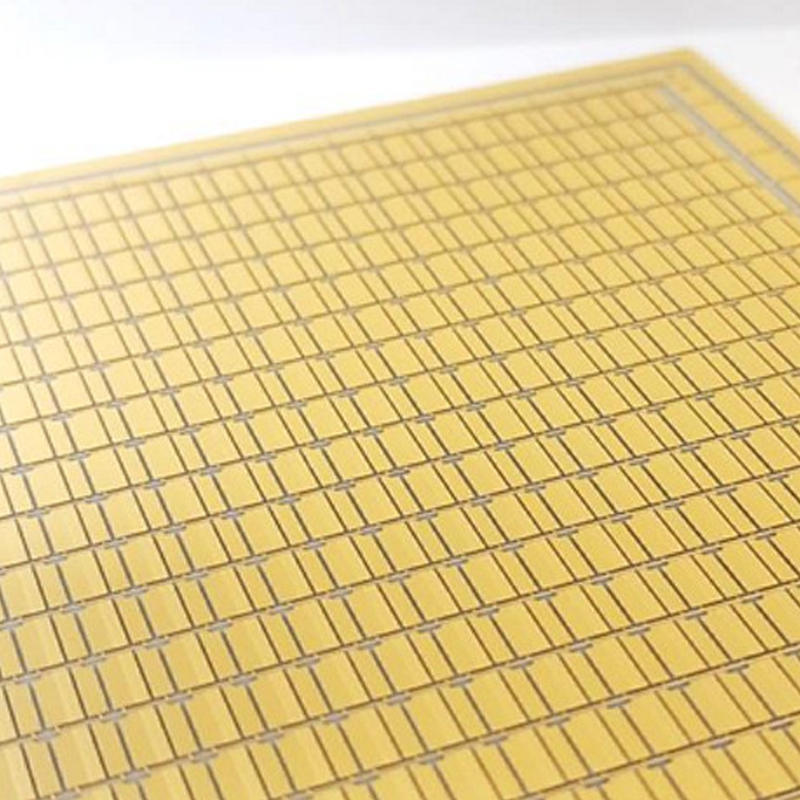

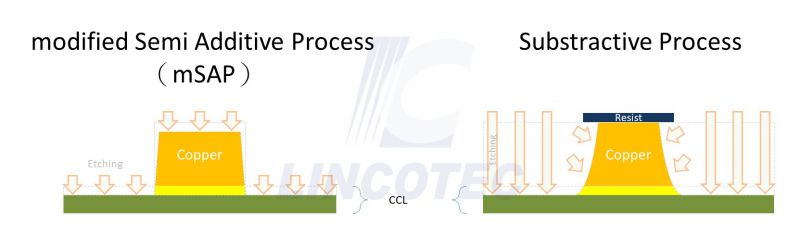

目前先進載板及高階PCB的線路製程工藝主要為三種技術,分別是減成法(Substractive Process)、加成法(Additive Process),與半加成法(modified Semi Additive Process;mSAP)。

減成法是指將銅箔基板(Copper Clad Laminate;CCL)表面的無用銅層減除掉,進而製成電路板的成熟做法,缺點是蝕刻過程可能有銅層的側蝕問題,而導致線寬線距較小時會出現良率問題。

加成法的製程恰好相反,其是在無銅底基板上,直接以曝光顯影程序形成銅線路圖形,再透過化學銅增厚到需要的厚度。相對於減成法,加成法雖然更適合製作精細線路。但製程設備的建置成本較高,且由於使用不同的基板材料,將衍生較長的製造學習曲線並導致更高的技術進入壁壘。

半加成法製程則結合加成法與減成法的加工的特點。其使用銅箔層厚度較薄的銅箔基板,首先在銅箔基板上覆蓋光阻劑,經曝光顯影製作出線路圖形並露出底下的銅箔層,再以電鍍銅方式增厚線路部分的銅層厚度,最後去除光阻層及蝕刻除去多餘的銅箔層,此時,由於半加成法製程是使用銅箔層較薄的銅箔基板,因此蝕刻耗時較短而能減少產生線路側向蝕刻問題,故半加成法相較於減成法可以製造較小尺寸的電路圖形,進而實現更高效的電路性能。

隨著智慧型手機、平板電腦和其他可攜式裝置的普及,對於輕薄且高效能的電子產品需求也越來越高,於不斷縮小線寬線距的同時,對於線路的尺寸和形狀有較高的限制,這促使前瞻技術開發人員不斷探索更精密、更高效、更經濟的製程技術。導入凌嘉科技高選擇比、高均勻性的蝕刻技術,能夠準確地去除多餘的金屬材料而不損害其他部分,進而製作出精確的電路圖形,進一步還能整合性能優異的薄膜濺鍍設備,解決金屬附著力、鍍膜均勻性等問題,並以高產能進行生產,提高產品良率及競爭力。

對此,凌嘉科技有自主的智慧財產權,能協同客戶進行製程開發及實驗驗證,尤其於重佈線層製程應用中,對於Desmear、Descum、Ti etching、Seel layer濺鍍…等技術有豐富的製程開發經驗,除了可以提供研發階段於不同製程配方下的打樣服務之外,亦擁有合格且高精密度的實驗室能進行樣品的測試。