晶背金屬化是在電子設備製造過程中,在半導體基板(如矽晶片)或IC的背面以真空濺鍍的方式沉積一層或多層金屬層的工藝。該金屬層可做為接合/導熱用的金屬層,也可再接合基材,用於改善散熱、提供電屏蔽並降低電阻。

晶背金屬化的濺鍍製程的優劣對於產品良率及半導體元件的可靠性影響很大,如果金屬層與產品接合度不佳會造成金屬層剝離與阻抗上升等問題。低歐姆接觸電阻和出色的薄膜附著力是背面金屬化工藝最關鍵的要求。

應用說明

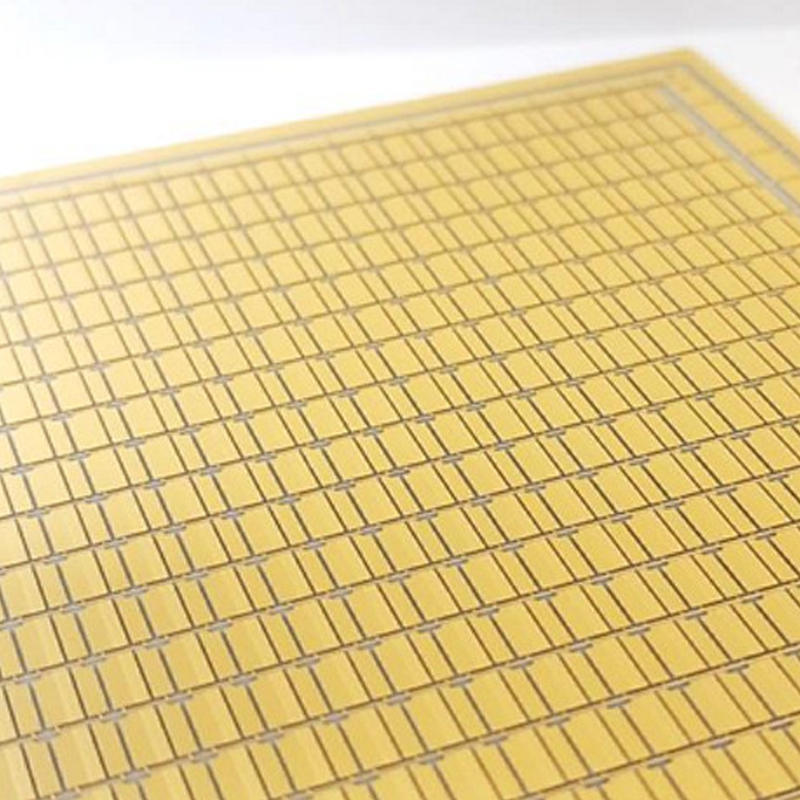

隨著科技的日新月異,5G通訊、物聯網(Internet of Things;IoT)、自駕車、先進醫療、智慧城市等智慧應用領域蓬勃發展,用於高速運算與高速傳輸之高速運算晶片(High Performance Computing;HPC)成為不可或缺的主角。為了解決運算中所累積的熱能,晶背金屬化(Backside Metallization;BSM)的產品應運而生。其是由BG、BM這兩個連續製程工藝所達成;首先研磨晶背(Backside Grinding;BG),減小其厚度,並讓表面略帶有粗糙度後,接著再沉積一層或多層金屬層(Backside Metallization;BM)做為接合或導熱用的金屬層,其步驟包括:

常見的種子層(Seed layer)為鈦(Ti)/鉻(Cr),而金屬層(Metal layer)則以鋁(Al)/銅(Cu)/鎳(Ni)/銀(Ag)/金(Au)或其合金的組合為主要。種子層與金屬層之間,還可視兩層金屬之特性,而再鍍上一中間層。舉例來說,高速運算晶片的晶背金屬化通常由鈦層與金層組成,而功率器件(Power Device)的晶背金屬化則通常由三層組成:鈦層(20-200nm)/鎳釩合金或純鎳層(200-400nm)/銀層(100-2000nm)。鈦層是種子層,鎳釩合金或純鎳層是矽基材和焊接材料之間的擴散屏障,而銀層可確保最佳焊接潤濕性並防止焊接前的鎳層氧化。

鈦底層被廣泛用於晶背金屬化技術,作為確保與矽基板的高附著力的材料。然而,根據晶圓表面條件、晶圓表面預處理技術和薄膜濺鍍工藝的參數,附著強度可能存在本質差異。為了減少晶圓的額外翹曲,濺鍍製程中除了需要溫和及精確的處理外,還需要對薄膜堆疊進行有效的應力控制,特別是通常在晶片應力分佈不均勻的情況下發生的“馬鈴薯碎裂”。此外,為了避免薄化後的晶片產生熱變形,於此製程中,除了無法加熱晶圓以提高薄膜的附著力之外,進一步還必需改進製程的熱排除能力,此亦將增加設備製造的難度。

BSM濺鍍製程的優劣對於產品良率及半導體元件的可靠性影響很大,如果金屬層與產品接合度不佳會造成金屬層剝離與阻抗上升等問題。低歐姆接觸電阻和出色的薄膜附著力是背面金屬化工藝最關鍵的要求。

對此,凌嘉科技有自主的智慧財產權,能協同客戶進行製程開發及實驗驗證,尤其於晶背金屬化製程應用中,對於晶圓的表面預處理、低溫種子層濺鍍、低溫金屬層濺鍍…等技術有豐富的製程開發經驗,除了可以提供研發階段於不同製程配方下的打樣服務之外,亦擁有合格且高精密度的實驗室能進行樣品的測試。