随着智能型手机、平板电脑和其他可携式设备的普及,对于轻薄且高性能的电子产品须求也越来越高,於缩小线宽线距的同时,线路的尺寸和型状有越来越高的限制,这促使前瞻技术开发人员不断探索更精密、更高效、更经济的制程技术。

导入凌嘉科技高选择比、高均匀性的蚀刻技术,能够准确地去除多余的金属材料而不损害其他部分,进而制作出精确的电路图形,进一步还能整合性能优异的薄膜溅镀设备,解决金属附着力、镀膜均匀性等问题,提高产品良率及竞争力。

应用说明

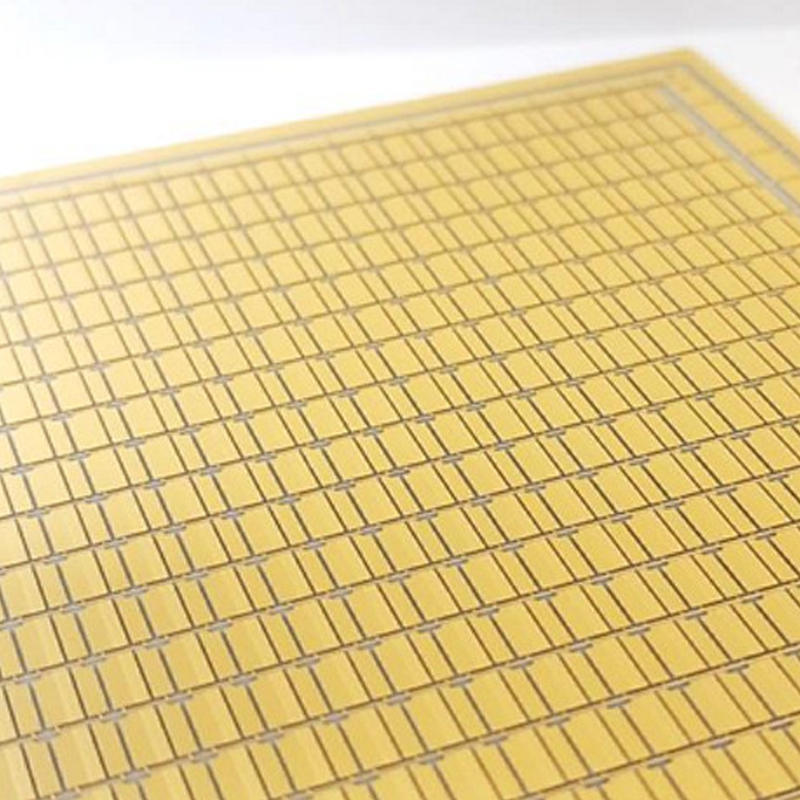

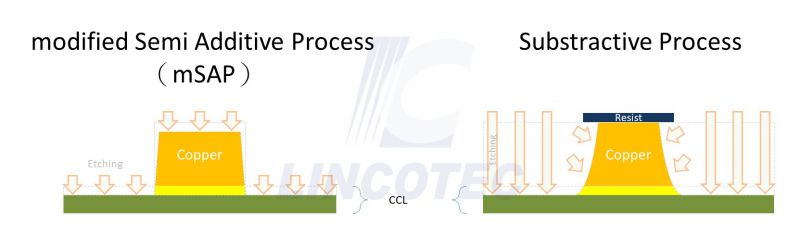

当前先进载板及高端PCB的线路制程工艺主要为三种技术,分别是减成法(Substractive Process)、加成法(Additive Process),与半加成法(modified Semi Additive Process;mSAP)。

减成法是指将铜箔基板(Copper Clad Laminate;CCL)表面的无用铜层减除掉,进而制成电路板的成熟做法,缺点是蚀刻过程可能有铜层的侧蚀问题,而导致线宽线距较小时会出现良率问题。

加成法的制程恰好相反,其是在无铜底基板上,直接以曝光显影进程形成铜线路图形,再透过化学铜增厚到需要的厚度。相对于减成法,加成法虽然更适合制作精细线路。但制程设备的建置成本较高,且由于使用不同的基板材料,将衍生较长的制造学习曲线并导致更高的技术进入壁垒。

半加成法制程则结合加成法与减成法的加工的特点。其使用铜箔层厚度较薄的铜箔基板,首先在铜箔基板上复盖光阻剂,经曝光显影制作出线路图形并露出底下的铜箔层,再以电镀铜方式增厚线路部分的铜层厚度,最后去除光阻层及蚀刻除去多余的铜箔层,此时,由于半加成法制程是使用铜箔层较薄的铜箔基板,因此蚀刻耗时较短而能减少生成线路侧向蚀刻问题,故半加成法相较于减成法可以制造较小尺寸的电路图形,进而实现更高效的电路性能。

随着智能型手机、平板电脑和其他可携式设备的普及,对于轻薄且高性能的电子产品须求也越来越高,於不断缩小线宽线距的同时,对于线路的尺寸和型状有较高的限制,这促使前瞻技术开发人员不断探索更精密、更高效、更经济的制程技术。导入凌嘉科技高选择比、高均匀性的蚀刻技术,能够准确地去除多余的金属材料而不损害其他部分,进而制作出精确的电路图形,进一步还能整合性能优异的薄膜溅镀设备,解决金属附着力、镀膜均匀性等问题,并以高产能进行生产,提高产品良率及竞争力。

对此,凌嘉科技有自主的知识产权,能协同客户进行制程开发及实验验证,尤其於重布线层制程应用中,对于Desmear、Descum、Ti etching、Seel layer溅镀…等技术有丰富的制程开发经验,除了可以提供研发阶段於不同制程配方下的打样服务之外,亦拥有合格且高精密度的实验室能进行样品的测试。品的测试。