超越摩尔定律的先进封装

因应人工智能、高速通信技术(5G、Wifi6)、高效数据中心、汽车电子…等新兴科技产品须求,能够达到高传输速度、高信号品质,且低延迟的封装技术将是非常重要的课题,这必须仰赖先进材料及不断地精进制程设备的能力,方能突破至更微细的整体生产工艺。同时,新世代的制程设备除了制造出符合性能要求之外,进一步还须兼顾环保议题,为企业的永续尽一份力。

凌嘉科技的薄膜溅镀及电浆蚀刻平台以干式环保制程为技术核心,除了设备能力能够满足客户的要求,亦能提供客制化的自动化平台,达到高良率、高产能的最低生产成本(COO)之优势。在半导体先进封装领域中,我们至少拥有下述的设备应用知识与能力,并具有厚实的专业能力而能借由相似的制程模式衍伸至其他的制程应用。

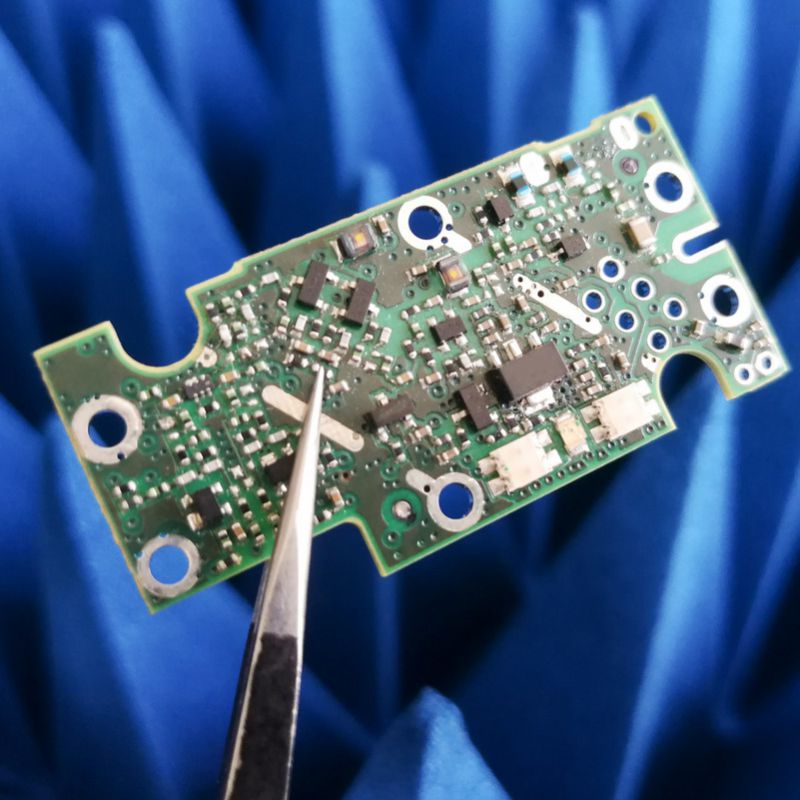

每个电子组件或其系统在运作时都会生成一定程度的电磁干扰 (EMI),这会对周边电器的性能生成不利影响。因此,电子组件或其系统的电磁干扰必须受到限制,同时,对环境中的干扰也必须具有足够的免疫力。

“抗电磁干扰屏蔽溅镀”即是以干式制程於电子组件的外表面以物理的方式附着上足够厚度的屏蔽层,借此达到电磁屏蔽的目的。

後摩尔定律(Moore‘s Law)时代,前段制程的研发及设备成本大幅提升,采用先进封装以进一步提高芯片整合度并降低制造成本,已是半导体展业变革趋势。

扇出型封装技术包括FOWLP与FOPLP,共同点是能以扇出的形式形成较多的I/O引脚,借此使单一芯片能整合更多功能,并达到薄型化及降低成本等优点。两者主要差异在于生产时的载体不同,进而能依芯片用途而选择於细线路尺寸及封装成本之间的平衡。

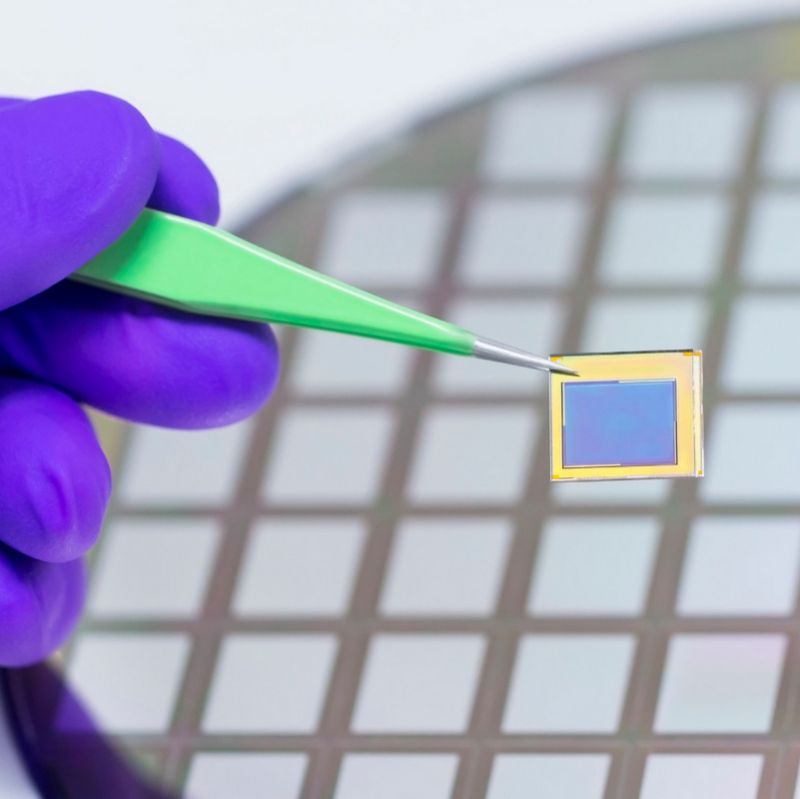

以先进半导体制程技术制造出的“已知良好裸晶(Know Good Die;KGD)”,通常拥有较高的线路密度,而必须借由扇出(Fan out)的方式将线路接点(I/O Pad)自裸晶表面的狭小区域向外重新布置,以利后续的芯片装配。

重分布线层(Redistribution Layer;RDL)即是利用晶圆等级的金属布线技术将线路接点外引至芯片外,同时达到更薄的封装厚度及更优异的电性表现。

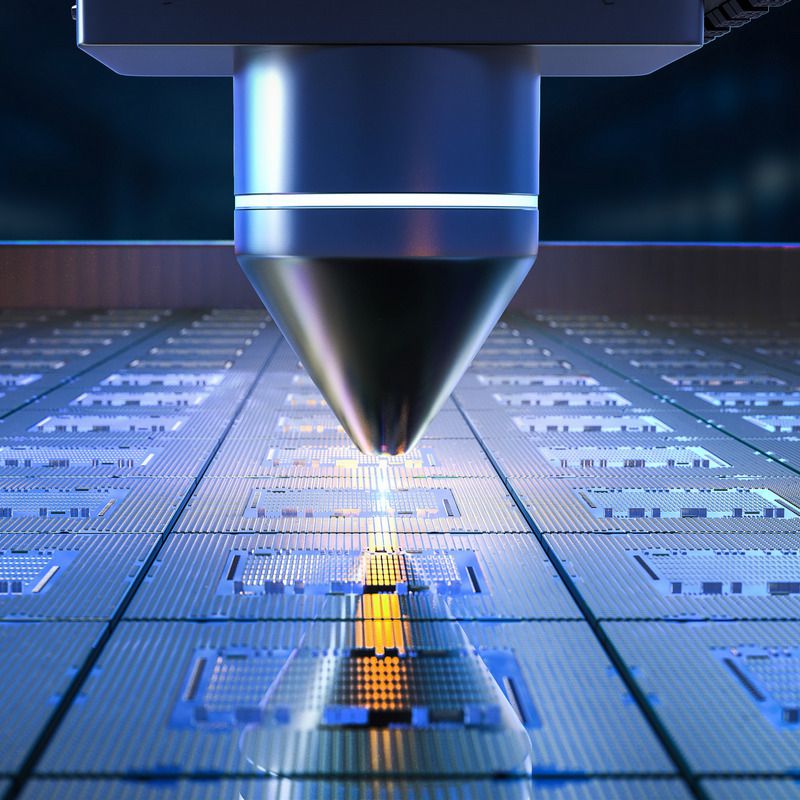

随着智能型手机、平板电脑和其他可携式设备的普及,对于轻薄且高性能的电子产品须求也越来越高,於缩小线宽线距的同时,线路的尺寸和型状有越来越高的限制,这促使前瞻技术开发人员不断探索更精密、更高效、更经济的制程技术。

导入凌嘉科技高选择比、高均匀性的蚀刻技术,能够准确地去除多余的金属材料而不损害其他部分,进而制作出精确的电路图形,进一步还能整合性能优异的薄膜溅镀设备,解决金属附着力、镀膜均匀性等问题,提高产品良率及竞争力。

无导线电镀金技术(Non Plating Line;NPL)提供了一种不需要在载板的表面布设电镀用导线,即可以对载板边缘的接触垫(Pad)进行电镀镍金的设计。其主要以导电膜作为电流传导路径以导通载板上的各接触垫,进而对其进行电镀镍金的工艺与结构,可大幅度减少因电镀导线的布设而造成的影响。

晶背金属化是在电子设备制造过程中,在半导体基板(如矽芯片)或IC的背面以真空溅镀的方式沉积一层或多层金属层的工艺。该金属层可做为接合/导热用的金属层,也可再接合基材,用于改善散热、提供电屏蔽并降低电阻。

晶背金属化的溅镀制程的优劣对于产品良率及半导体组件的可靠性影响很大,如果金属层与产品接合度不佳会造成金属层剥离与阻抗上升等问题。低欧姆接触电阻和出色的薄膜附着力是背面金属化工艺最关键的要求。

相较于有芯载板(Cored Substrate),无芯载板(Coreless Substrate)技术取消了作为核心层的玻纤布,而改以直接使用增层绝缘材料进行布线封装。

无芯载板技术借由取消核心层而降低成本,此外因布线能力的提高,使得锡球凸块的布局限制极小,并能达到良好的高速传输特性,於交流和直流功率特性均能得到改善。