以先进半导体制程技术制造出的“已知良好裸晶(Know Good Die;KGD)”,通常拥有较高的线路密度,而必须借由扇出(Fan out)的方式将线路接点(I/O Pad)自裸晶表面的狭小区域向外重新布置,以利后续的芯片装配。

重分布线层(Redistribution Layer;RDL)即是利用晶圆等级的金属布线技术将线路接点外引至芯片外,同时达到更薄的封装厚度及更优异的电性表现。

应用说明

随着微缩技术的进步及芯片功能的复杂化,以先进半导体制程技术制造出的“已知良好裸晶(Know Good Die;KGD)”,因具有极高的晶体管密度及线路密度,而无法在裸晶的面积之内容纳所有的接脚,必须借由扇出(Fan out)的方式将线路接点(I/O Pad)自裸晶表面向外重新布置,借此符合封装和其他电路的要求。

而将金属线路接点外引的技术,即泛称为重布线层(Redistribution Layer;RDL)技术。於应用上又可依线宽间距(Line/Space;L/S)进一步分为:(1)晶圆厂的超细线路应用;(2)先进封装厂的细线路应用;及(3)先进载板厂的细线路应用。

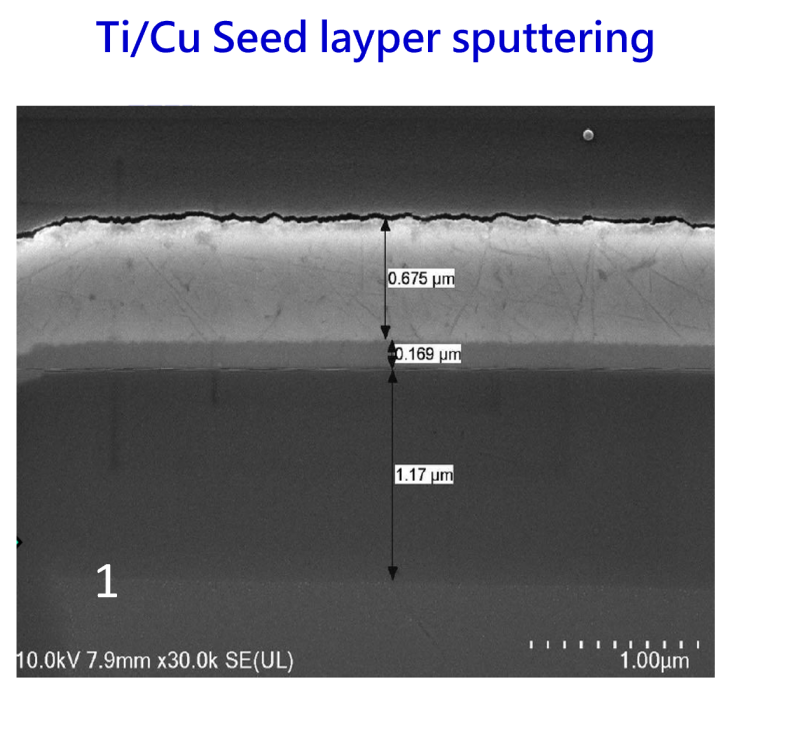

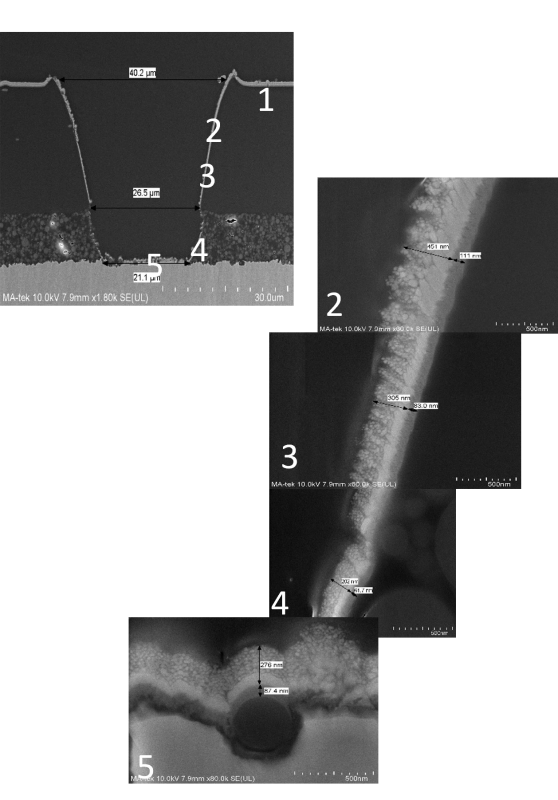

於不同的应用中,会采用不同制程解决方案来完成金属导线的制作,例如利用光罩以曝光、显影、蚀刻的方式制造出超细线路,或者是使用雷射光刻配合清洁、溅镀金属种子层、电镀增厚金属层、蚀刻去除金属种子层的方式於基材上制造出金属细线路。前者可达成超细线路的应用但设备成本较高而多见于晶圆厂,后者则通常用于封装厂或载板厂。

进一步在ESG的政策响应下,后者也逐步从湿式制程转换至干式制程,例如基材的清洁方式改以干式的电浆蚀刻清洁;而蚀刻去除种子层的方式,也从利用药水的湿式制程逐步朝向以干式电浆蚀刻的方式将其去除,借此达到低材料消耗、低环境污染和简单的後处理工序目的。

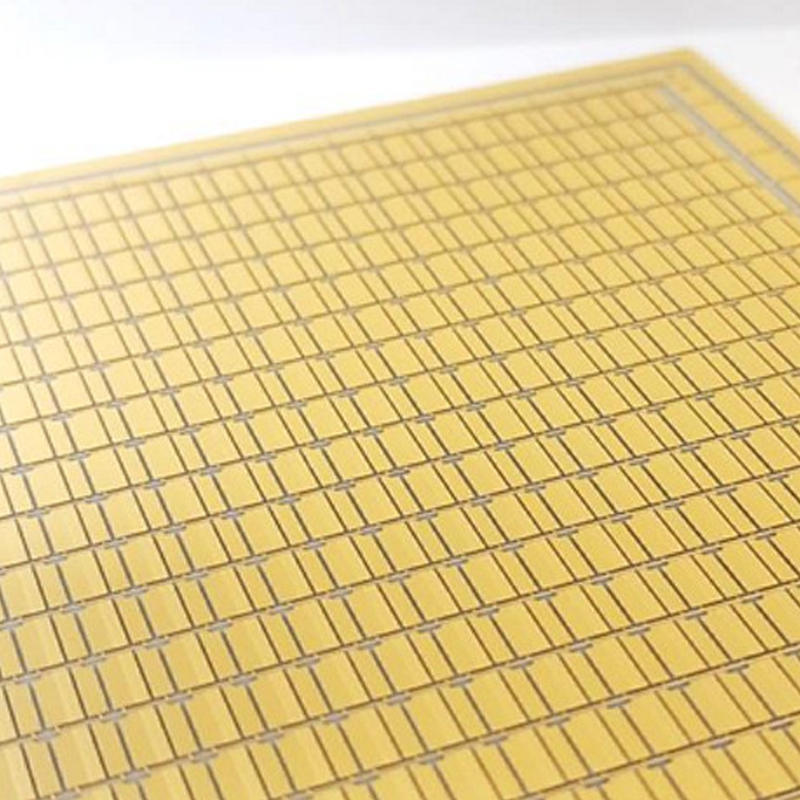

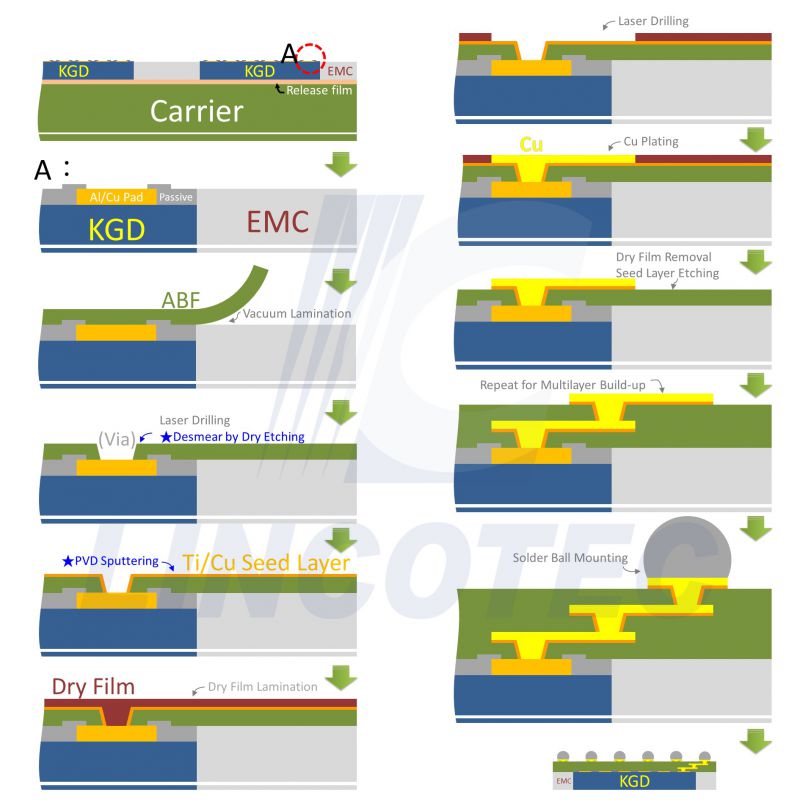

以下图标说明先进封装厂以ABF(Ajinomoto Build-up Film)作为基材时的Die-First/Face-up重布线层制程:

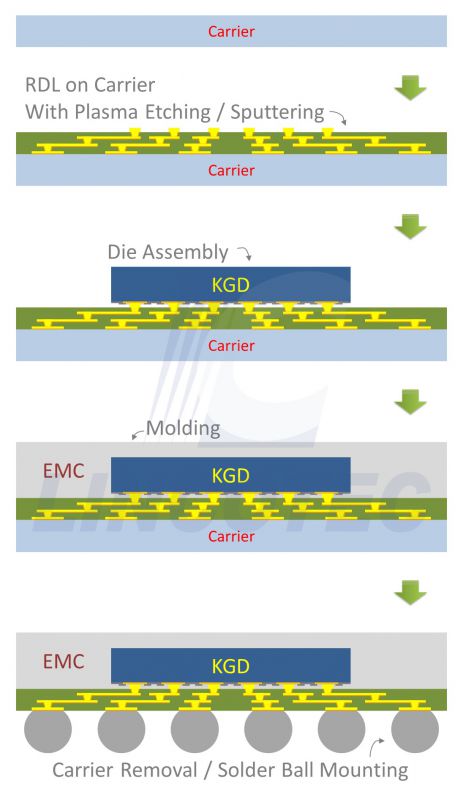

前述的Die Fisrt制程由于是直接先放置KGD之后,再对其进行重布线。但这样的制程可能因制程良率的风险而导致KGD的损坏,因此尚有另一种先完成RDL之后,再将KGD附着上去的Die-last制程,如下图所示。虽然相较于Die-first制程,此方式需先以Carrier当作临时的载体,再至将其移除后于同侧附着锡球,制程步骤略为复杂,但能有效避免KGD的损失。

对此,凌嘉科技有自主的知识产权,能协同客户进行制程开发及实验验证,尤其於重布线层制程应用中,对于Desmear、Descum、Ti etching、Seel layer溅镀…等技术有丰富的制程开发经验,除了可以提供研发阶段於不同制程配方下的打样服务之外,亦拥有合格且高精密度的实验室能进行样品的测试。

凌嘉特色

专注於Sputter及Etching技术,掌握RDL的关键能力

实绩