後摩尔定律(Moore‘s Law)时代,前段制程的研发及设备成本大幅提升,采用先进封装以进一步提高芯片整合度并降低制造成本,已是半导体展业变革趋势。

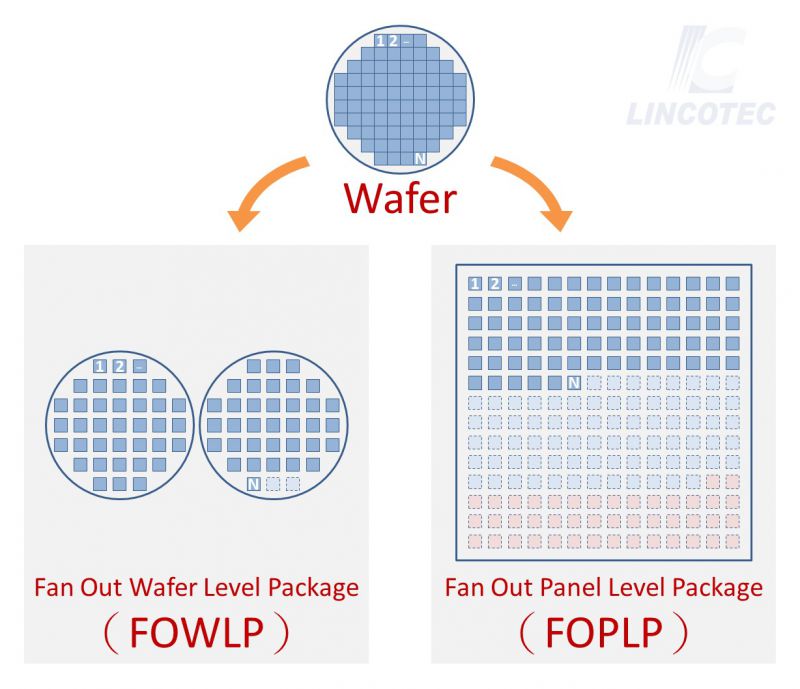

扇出型封装技术包括FOWLP与FOPLP,共同点是能以扇出的形式形成较多的I/O引脚,借此使单一芯片能整合更多功能,并达到薄型化及降低成本等优点。两者主要差异在于生产时的载体不同,进而能依芯片用途而选择於细线路尺寸及封装成本之间的平衡。

应用说明

传统的摩尔定律(Moore's law)通常被解读为:单位面积的集成电路上可容纳的晶体管数目约每隔2年会增加1倍;同样运算速度的芯片价格则每2年会变成2分之1。但随着晶圆制造厂(Foundry)的前段先进制程技术逐渐进入物理极限,且为超高资本投资,穷尽资源追求前段制程的微缩已非半导体产业的唯一手段。

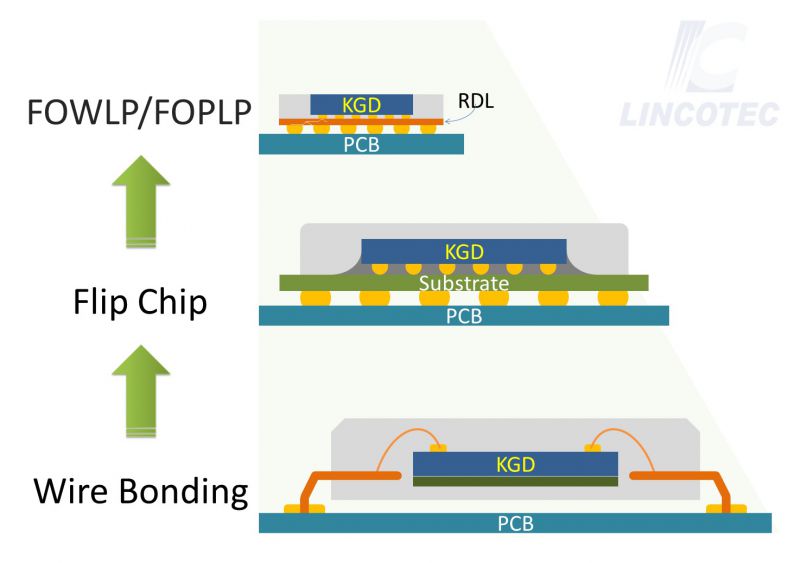

先进封装制程的发展,自早期的打线接合技术(Wire Bonding) 、覆晶技术(Flip Chip) ,再到当前的扇形封装技术(Fan Out),自是不断尝试使芯片能够堆栈或缩小相邻芯片的间距,而使芯片之间的金属连接(Interconnect)距离变短,借此缩小尺寸与缩短信号传输距离而取得较佳的电性表现。

为达以上目的,还需借由良好的制程流程规划及设备参数以降低其线路阻抗(RC, Contact resistance)而进一步提高其性能及可靠度。如此方能满足後摩尔时代於消费性电子产品不断增长的须求,及提供定价时的有利PPAC指针:“高功率(Power)、高性能(Performance)、低芯片面积(Area)、低成本(Cost)”。

早期的打线接合技术是将IC芯片固定于导线架(Lead Frame)上,再以例如金线等焊线连接芯片与外引脚之间,其缺点除了必须“一根一根地”打线之外,由于导线架的金属接脚只能制作在四周围,所以当芯片的接脚须求提高时,将增加封装体积且将提高焊线的材料成本,并不利用在日益要求重量、尺寸及多元功能的消费型电子产品上。

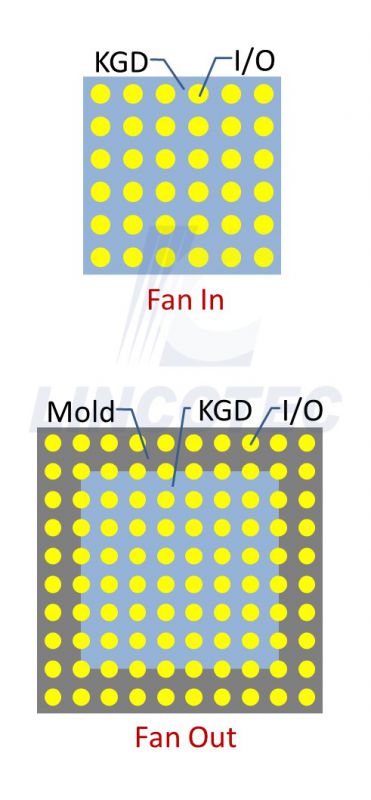

1960年代,美国IBM公司提出以覆晶形式的芯片接合方式,是先于矽芯片上以晶圆级构装(Wafer Level Package;WLP)布线,并采用Fan in设计形成位于芯片范围内之金属凸块(Bump),及位于凸块上的金属焊材,此时。金属焊材能加热而形成球状,进而当芯片与电路板连接时能依其物理性质而具自我校正位置的功效,借此提高良率并用於细小节距(Fine Pitch)的产品上。由于覆晶技术具有高I/O密度、易于电磁屏蔽处理、低电感、封装尺寸小等优点,已成为当前市占率最高之封装技术。

进一步,德国英飞凌公司(Infineon Technologies)於2001年提出US6727576B2专利,为扇出型晶圆级封装(Fan Out Wafer Level Package;FOWLP)技术之滥觞。节录SEMI国际半导体产业协会于其官网之说明:“FOWLP技术是从半导体裸晶的端点上,向外拉出需要的电路至重分布层(Redistribution Layer;RDL),进而形成封装。其最大的特点在于:在尺寸相同的芯片下让重分布层范围更广,芯片脚数更多,单芯片可以整合更多功能,并达到无载板封装、薄型化以及低成本等优点。若希望达到高密度量产的目标,重分布层的技术应用将是关键。

扇出型晶圆级封装的制程可分为以下两种主流:

1.芯片优先Fan Out:於基板上放置,从原始设备晶圆中挑拣出的合格晶元(Know Good Die;KGD),以模压树脂包复成重构晶圆,再进一步处理成晶圆上的RDL。

2.RDL优先Fan Out:载具晶圆顶端创建RDL层并暂时接合,在顶端放置KGD然后研磨压模与模具。

扇出型晶圆级封装技术仍是基于前段半导体制程,惟因需提供向外扇出线路之空间,而必须将KGD重新取放(Pick and Place)至重构晶圆上,由于前后段制程能整合进行,相较于其他封装技术,除了能降低制程生产与材料等成本之外,针对低线宽间距(Line Space;L/S),还能整合步进式曝光机(Stepper)或光罩对准曝光机(Mask Aligner)达到高精度要求。

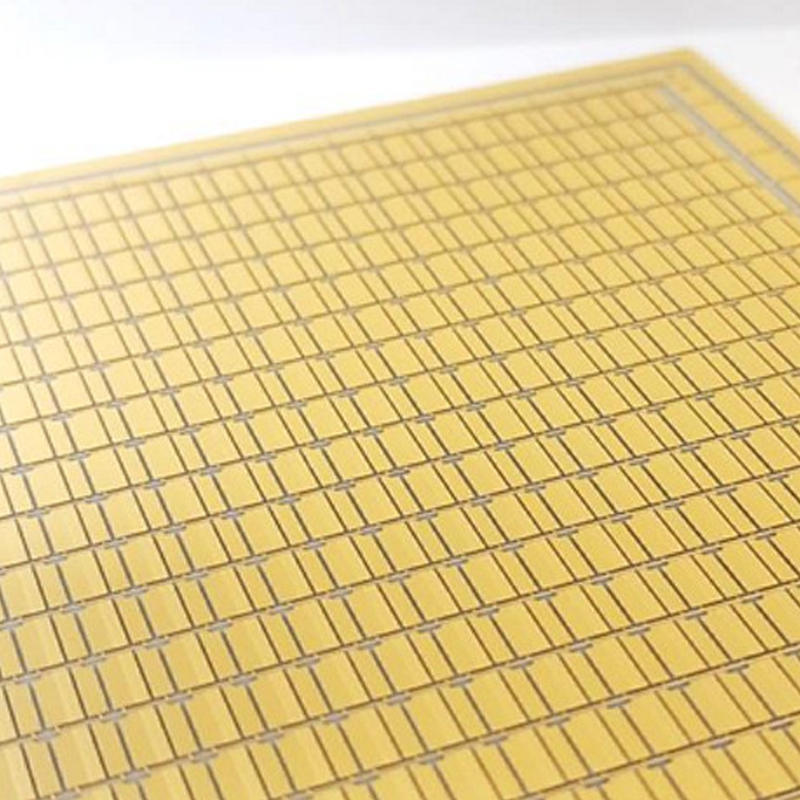

但并非所有的芯片於封装时都会要求低线宽线距,此时考量选用更多元的封装材料与成本更低的设备即为PPAC指针的关键。此外,每片重构晶圆能乘载的KGD数量有限,并不利于一次性的大量生产,因此衍生出了以面积更大的矩型载板,例如印刷电路板或是玻璃基板,作为载体进行扇出封装制程的扇出型面板级封装技术(Fan Out Panel Level Packaging;FOPLP)。

扇出型晶圆级封装与扇出型面板级封装同样具备提升电气性能与I/O密度、支持薄型化设计等优势,并期望能借由更大面积的生产进一步降低生产成本,从右图可以明显看出采用FOPLP时的产能优势。

以下整理扇出型晶圆级封装与扇出型面板级封装的特点比较:

| 扇出型晶圆级封装(FOWLP) | 扇出型面板级封装(FOPLP) | |

|---|---|---|

| 每片产能 | 受限于重构晶圆的尺寸,产能较低。 | 产能较高,以12寸晶圆与700x700mm2的载具相比较, 载具单次的产量约为晶圆的7.8倍。 |

| 应用领域 | I/O高密度要求之芯片,例如:CPU、GPU、 AP、ASIC、FPGA、AiP等。 | I/O密度要求较低之芯片,例如:PMIC、APE、MEMS、Sensor等。 |

| 设备须求 | 多采用较精密的先进制程设备,成本较高。 | 对于制程设备的精度要求相对较低,成本较低。 |

| 线宽线距 | L/S<5/5 | L/S≥5/5 |

| RDL层数 | 可达5层以上 | 多用于4层以下 |

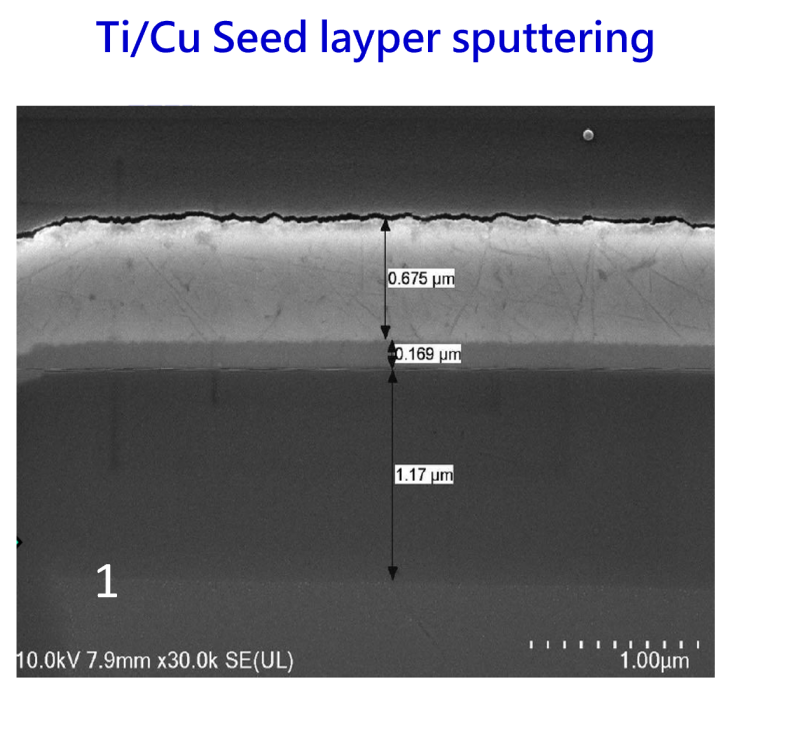

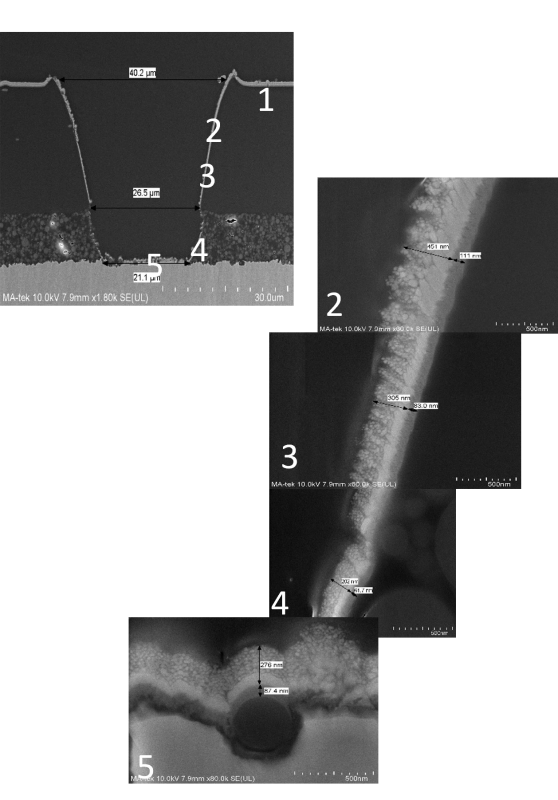

对此,凌嘉科技有自主的知识产权,能协同客户进行制程开发及实验验证,尤其於FOPLP领域中,对于Desmear、Descum、Ti etching、Seel layer溅镀…等技术有丰富的制程开发经验,除了可以提供研发阶段於不同制程配方下的打样服务之外,亦拥有合格且高精密度的实验室能进行样品的测试。

凌嘉特色

专注於Sputter及Etching技术,掌握FOPLP的关键能力

实绩